はじめに

鉛による環境汚染に対し警告規制の動きが起こり、特にEUでは電子製品全体からの有害物質全廃が法制化され、輸入製品全体が規制されています。アメリカ合衆国・カルフォルニア集では電子廃棄物リサイクル法SB50が法制化され、中国・韓国にも追従の動きがあり、全世界的に鉛フリーの潮流になっています。

この流れを受け、電子・電気機器製造分野では鉛フリーはんだの接合技術開発が急務となり、内部基板においてはBGA化が進められています。同時期に携帯電話・ゲーム機器の普及とノートパソコンのモバイル化が進み、電子・電気製品に対する耐落下衝撃性の要求も高まっています。

この要求に対し、各メーカーが個別にサプライヤに向けて衝撃耐性を要求していたが、米国電子工業会EIA(Electronic Industries Alliance)が主導し、JEDEC(Joint Electron Device Engineering Council)によるJEDEC規格が制定され、衝撃試験規格JEDEC22-B111が発行されました。

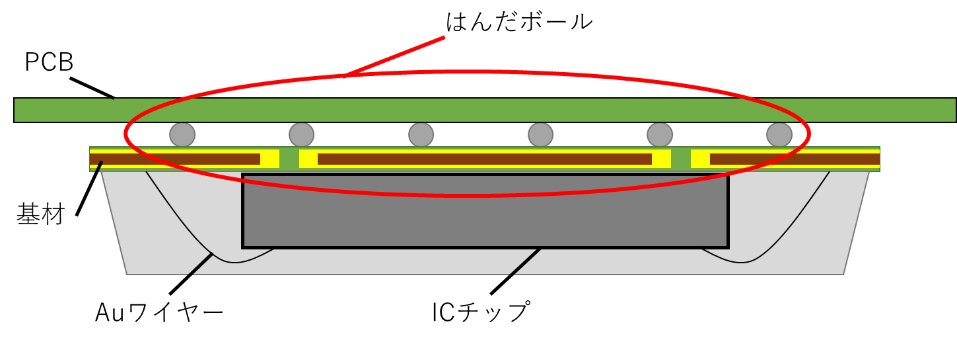

BGA(Ball Grid Array)基板の構造と導通評価

BGA基板はPCB(Printed Circuit Board)とICチップをはんだボールにより接合しています。基板に衝撃が発生すると基板がたわむことによりはんだボールの接合が外れ、通信信号が一瞬途切れる現象(以下、瞬断)が発生し、これが電子機器の不具合の原因となります。ここで、衝撃発生時に基板のたわみによる瞬断で導通が途切れた場合でも、衝撃発生後には基板のたわみが戻ることで導通が確認されることもあります。そのため、衝撃により瞬断が発生しているのにも関わらず試験実施後の評価で合格と判断される可能性があるため、適切な導通評価を実施するためには衝撃発生時の導通を常にモニタリング監視しておく必要があります。

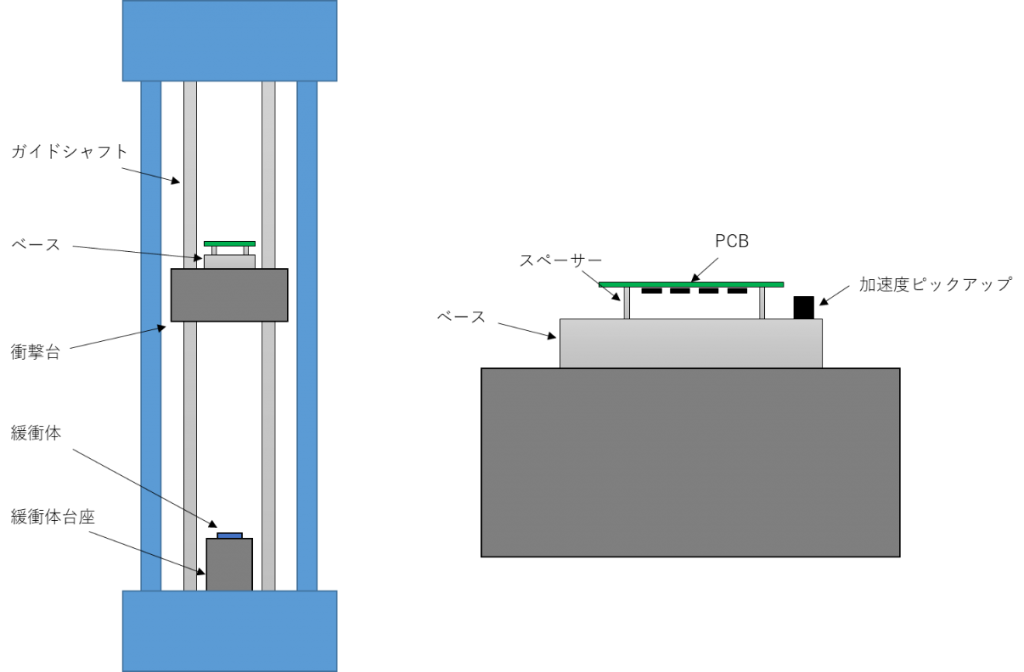

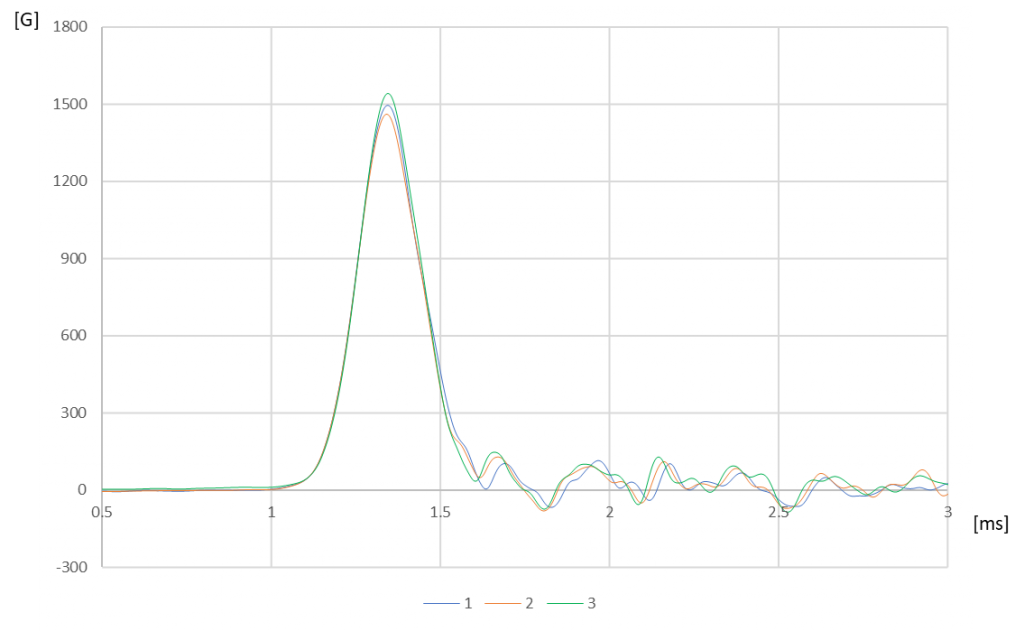

JEDEC規格に則った衝撃試験

JEDEC規格では1500G, 0.5msの衝撃波形が規定されており、規定の衝撃を正確に再現し、連続して精度よく発生させる装置が求められます。弊社製品である衝撃試験機HDST-150はJEDECの試験に特化した試験機であり、指定条件を高サイクルに発生させることが出来る仕様となっております。また、受託試験として利用できる衝撃試験機HDST-230も同様に1500G, 0.5msの衝撃を発生させることが出来るため、本装置に加速度計と導通評価器具を設置することで衝撃発生時の瞬断を正確に評価することが可能です。

詳細についてはお気軽にご相談ください。